IEEE Std 1800™-2012 (Revision of IEEE Std 1800-2009) IEEE Standard for SystemVerilog—Unified Hardware Design, Specification,

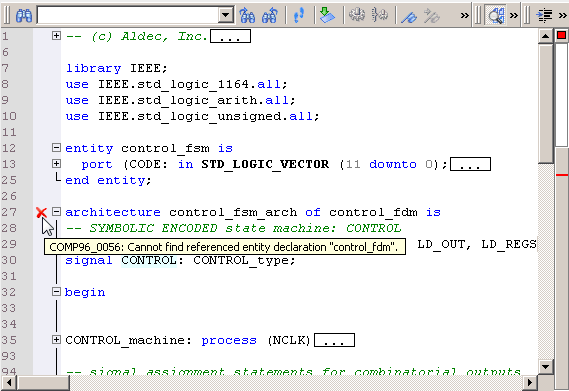

Setting up Source Code Analysis for SystemVerilog Compilation - Application Notes - Documentation - Resources - Support - Aldec

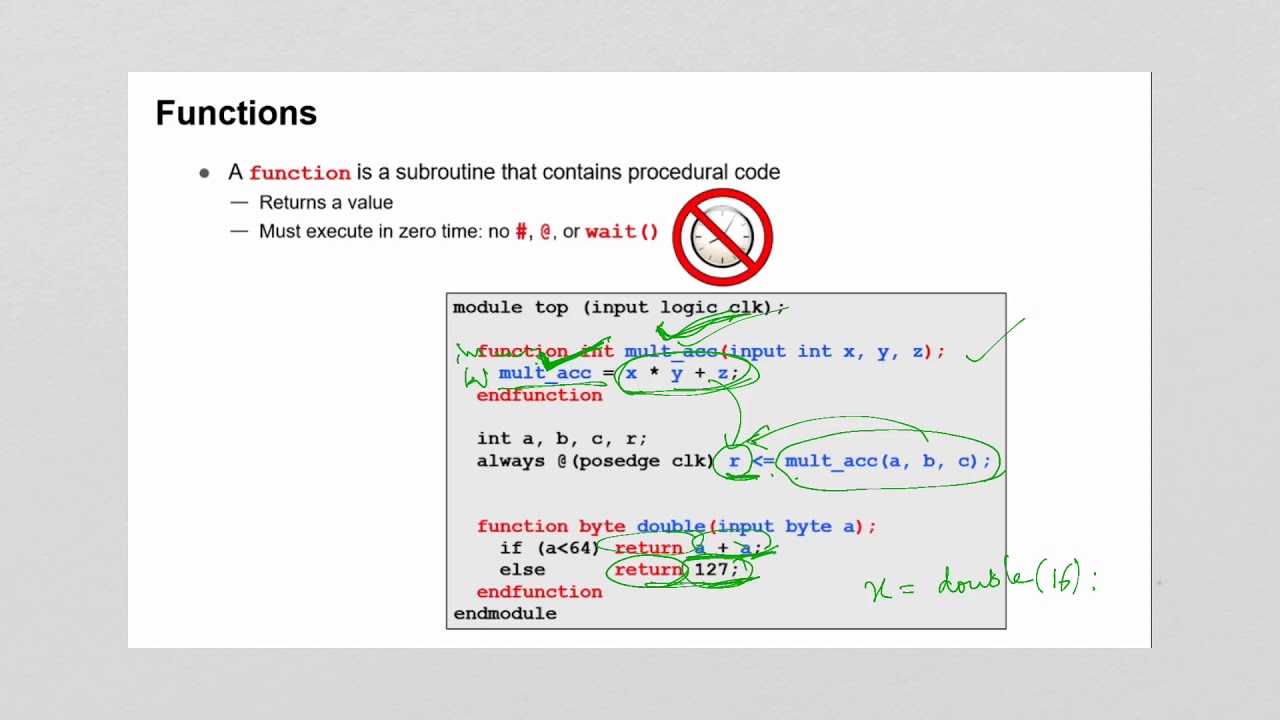

2. Functions and Tasks (call by reference) , automatic keyword, timescale in SystemVerilog - YouTube

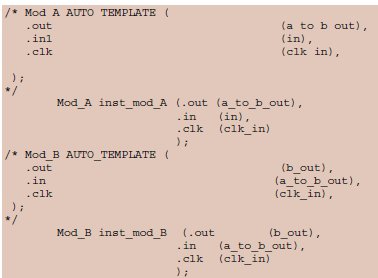

Automatic Generation of SystemVerilog Models from Analog/Mixed-Signal Circuits: A Pipelined ADC - YouTube

Save Time in Pre-Silicon Functional Verification Using Regression Automation Scripts | AMIQ Consulting

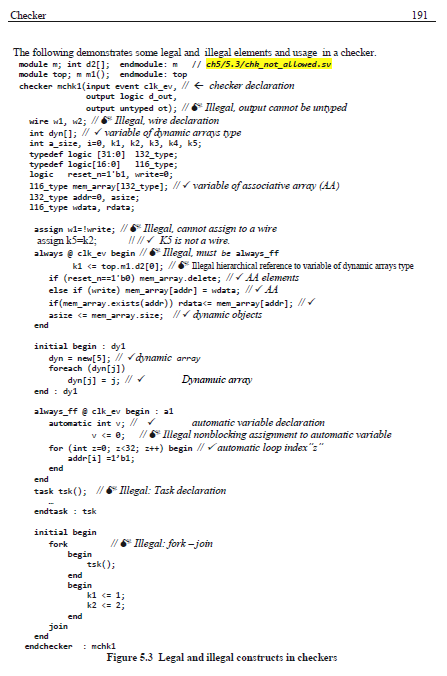

What kinda of assertions can be incorporated inside a Checker~endchecker block ?? Is it for dynamic variables ? | Verification Academy